Product Summary

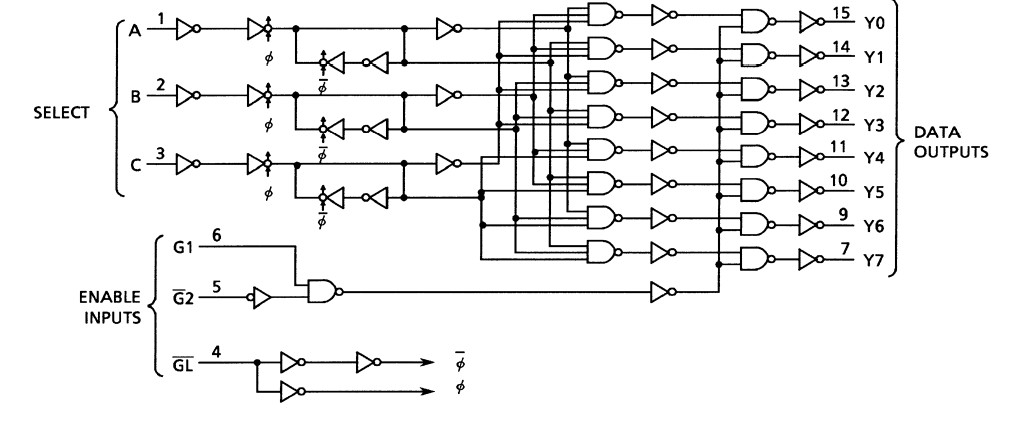

The 74HC237A is a high speed CMOS 3-to-8 line decoder address latch fabricated with silicon gate C2MOS technology. The 74HC237A achieves the high speed operation similar to equivalent LSTTL while maintaining the CMOS low power dissipation. All inputs of the 74HC237A are equipped with protection circuits against static discharge or transient excess voltage.

Parametrics

74HC237A absolute maximum ratings: (1)Supply voltage range VCC:0.5~7 V; (2)DC input voltage VIN: 0.5~VCC + 0.5 V; (3)DC output voltage VOUT:0.5~VCC + 0.5 V; (4)Input diode current IIK: ±20 mA; (5)Output diode current IOK: ±20 mA; (6)DC output current IOUT: ±25 mA; (7)DC VCC/ground current ICC: ±50 mA; (8)Power dissipation PD 500 (DIP): 180 (SOP)mW; (9)Storage temperature Tstg: 65~150 ℃.

Features

74HC237A features: (1)High speed: tpd = 12 ns (typ.)at VCC = 5 V; (2)Low power dissipation: ICC = 4 μA (max)at Ta = 25℃; (3)High noise immunity: VNIH = VNIL = 28% VCC (min); (4)Output drive capability: 10 LSTTL loads; (5)Symmetrical output impedance: |IOH| = IOL = 4 mA (min); (6)Balanced propagation delays: tpLH tpHL; (7)Wide operating voltage range: VCC (opr)= 2~6 V; (8)Pin and function compatible with 74LS237.

Diagrams

|

74HC |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74HC/HCT02 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74HC/HCT03 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74HC/HCT10 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74HC/HCT107 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74HC/HCT109 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))