Product Summary

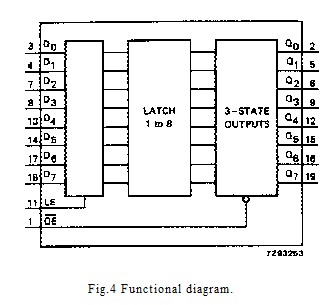

The 74HC373A is a high-speed Si-gate CMOS device and is pin compatible with low power Schottky TTL (LSTTL). It is specified in compliance with JEDEC standard no. 7A. The 74HC373A is an octal D-type transparent latches featuring separate D-type inputs for each latch and 3-state outputs for bus oriented applications. A latch enable (LE) input and an output enable (OE) input are common to all latches.

Parametrics

74HC373A absolute maximum ratings: (1)supply voltage: -0.5 to +7 V; (2)input clamping current: ±20 mA at VI < -0.5 V or VI > VCC + 0.5 V; (3)output clamping current: ±20 mA at VO < -0.5 V or VO > VCC + 0.5 V; (4)output current: ±35 mA at VO = -0.5 V to VCC + 0.5 V; (5)quiescent supply current: ±70 mA; (6)ground current: -70 mA; (7)storage temperature: -65 to +150 ℃; (8)total power dissipation: DIP20 package: 750 mW, SO20 package: 500 mW, (T)SSOP20 package: 500 mW, DHVQFN20 package: 500 mW.

Features

74HC373A features: (1)3-state non-inverting outputs for bus oriented applications; (2)Common 3-state output enable input; (3)Functionally identical to the "563", "573" and "533"; (4)Output capability: bus driver; (5)ICC category: MSI.

Diagrams

|

74HC |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74HC/HCT02 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74HC/HCT03 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74HC/HCT10 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74HC/HCT107 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74HC/HCT109 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))